DEPARTMENT OF COMPUTER & ELECTRICAL ENGINEERING

# EMC-Aware System Design - A focus on Integrated Circuits

Etienne SICARD Professor etienne.sicard@insa-toulouse.fr www.ic-emc.org INSA TOULOUSE - FRANCE

Airplanes

Rugby

- General context

- Integrated Circuits

- Electromagnetic

Compatibility

- Design Guidelines

# 1 GENERAL TRENDS

DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

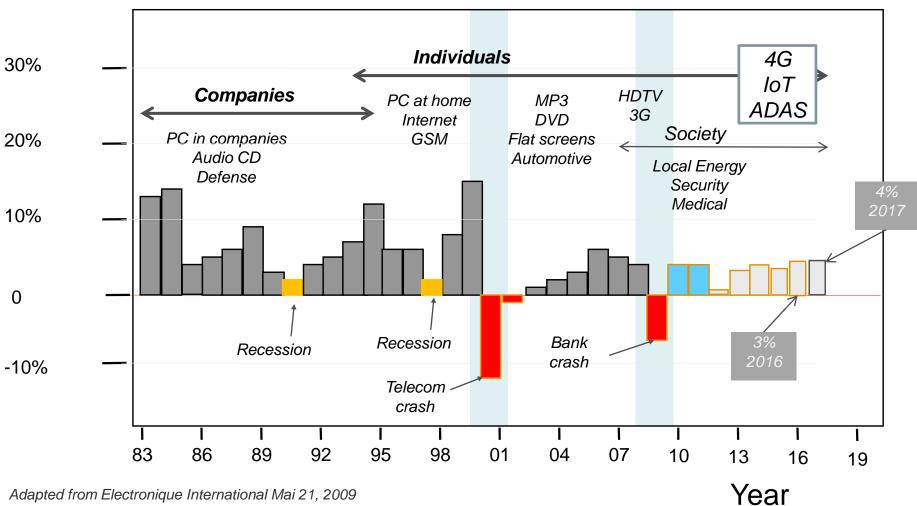

#### THE ELECTRONIC MARKET GROWTH

**Market Growth**

# MARKET GROWTH

Share of system sales

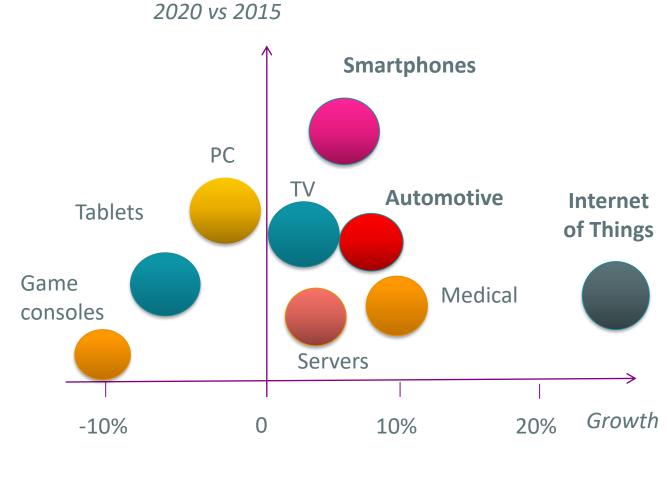

# **VISION 2020**

- Increasing disposable income,

- Expanding urban population,

- Growing internet

penetration and

- Availability of strong distribution network

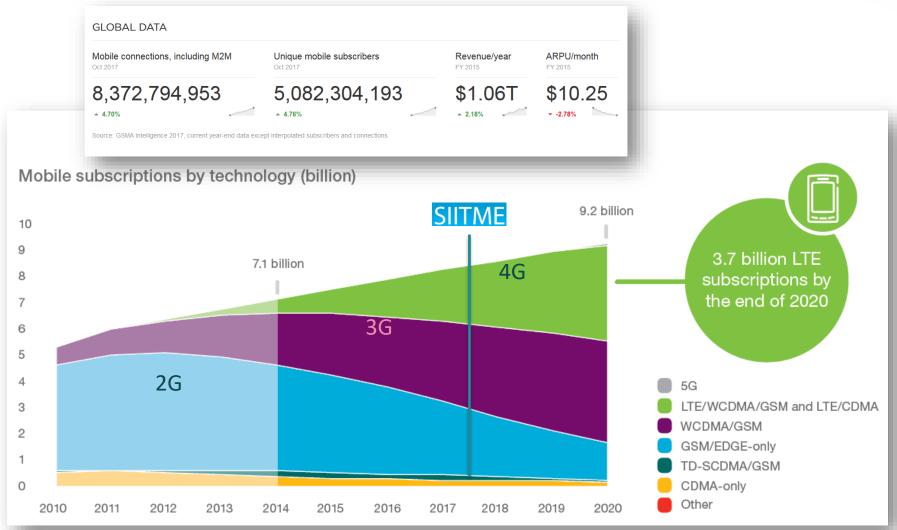

#### **MOBILE BUSINESS**

#### https://www.gsmaintelligence.com/

#### http://www.ericsson.com/ericsson-mobility-report

#### **INTERNET OF THINGS**

- Growth in 2016 was stalling (+5% smarthones)

- Consumer demand was sluggish (tablets, laptops).

- Demand for Internet of Things (IoT) ۲ wasn't growing fast enough to offset declines

- Price, security and ease-of-use remain barriers to the adoption of new IoT devices and services.

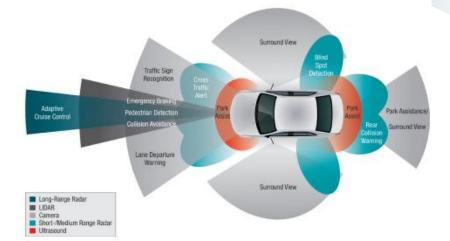

ADAS

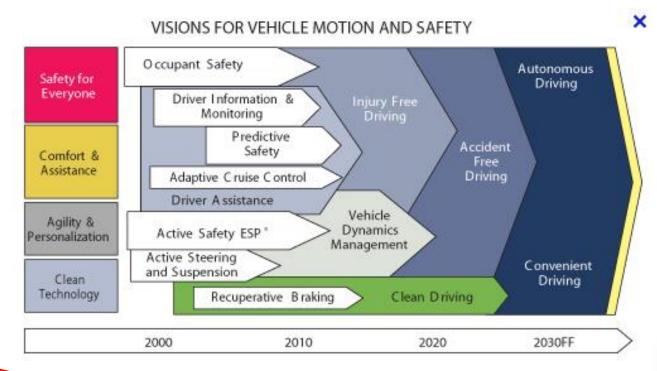

# TOWARDS AUTOMATIC DRIVE

- 2020 : Injury-free driving

- 2030: Accident-free driving ?

- 2040: Autonomous driving?

# 2 TECHNOLOGY TRENDS

DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

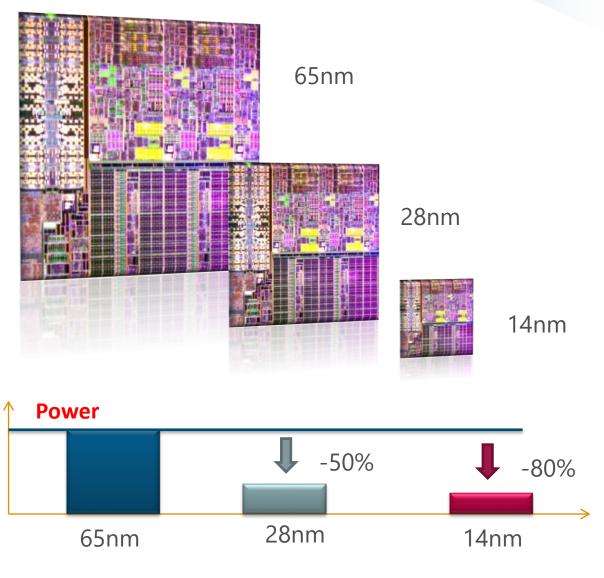

#### SCALE DOWN BENEFITS

- Smaller

- Faster

- Less power consumption

- Cheaper (if you fabricate millions)

- Room for other devices

Processors Memory

Security

Sensors

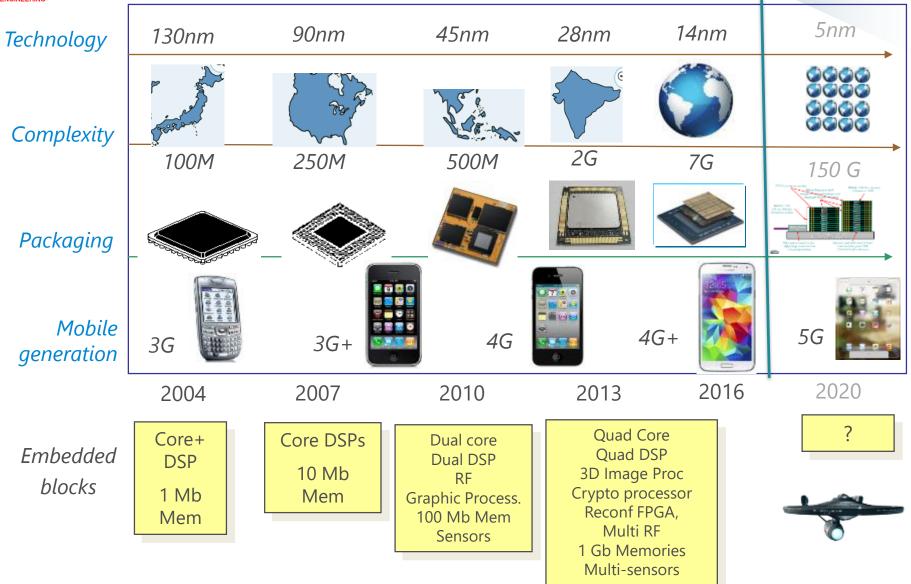

#### **MOBILE COMMUNICATIONS**

SIITME

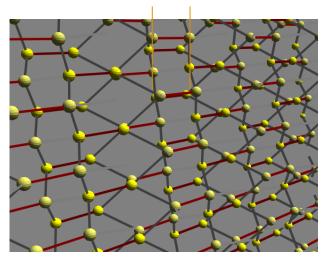

#### **GOING ATOMIC SCALE**

• 14-nm Xeon by Intel ™

• Qualcomm<sup>™</sup> Snapdragon X50

IBM, GlobalFoundries, Samsung,

SUNY first 7-nm testchip 2017

Si lattice: 0.23 nm

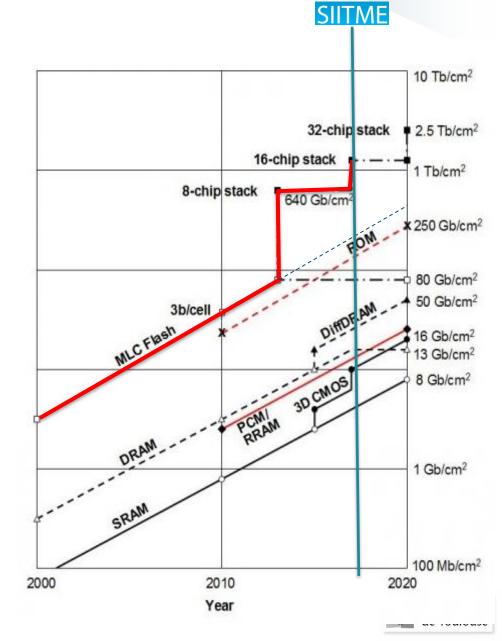

#### **GOING 3D - MEMORIES**

## **Stacked process layers**

- 8, 16, 32 layers of active devices

- 1 tera-bit/cm2 achieved 5 years ahead from roadmaps

| חודיוור           | חר חת                | זוראור | זרחור     |

|-------------------|----------------------|--------|-----------|

| Close-up image of | f V-NAND flash array |        | chipworks |

#

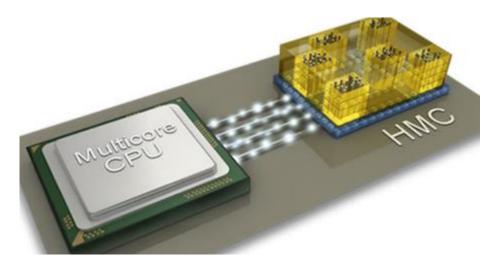

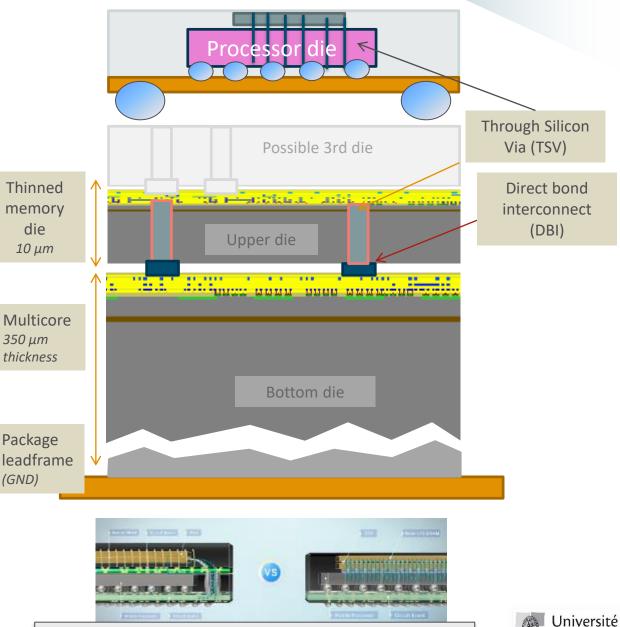

**3D IC TECHNOLOGY**

High Bandwidth Memory (HBM) Hybrid Memory Cube (HMC)

|                             | HBM2                                                                           | HMC Gen3                                                 |

|-----------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------|

| Density                     | 8 GB (4GB)                                                                     | 8 GB (4GB)                                               |

| Bandwidth                   | 256 GB/s                                                                       | 480 GB/s (320 GB/s)                                      |

| 10                          | Parallel (1G – 2G), 8 channels,<br>128b per channel                            | SerDes (up to 30G), 4(2) links per<br>HMC, 16 lanes/link |

| Package Type                | Si-interposer                                                                  | Discrete (SerDes)                                        |

| Expansion Capability        | No                                                                             | Yes, via chaining                                        |

| Memory Access               | DDR                                                                            | Packet based                                             |

| Power                       | Lower                                                                          | Higher                                                   |

| Memory Suppliers            | SK Hynix and Samsung                                                           | Only Micron                                              |

| Thermal Dissipation<br>Req. | High (Logic + DRAM in single<br>2.5D ASIC package)                             | Lower (discrete ICs)                                     |

| ldeal target markets        | Graphics, Networking, Less<br>frequently accessed<br>memory, Small form-factor | High-performance Computing,<br>Networking                |

http://www.eejour nal.com/article/20 170102-hbm-hmc/

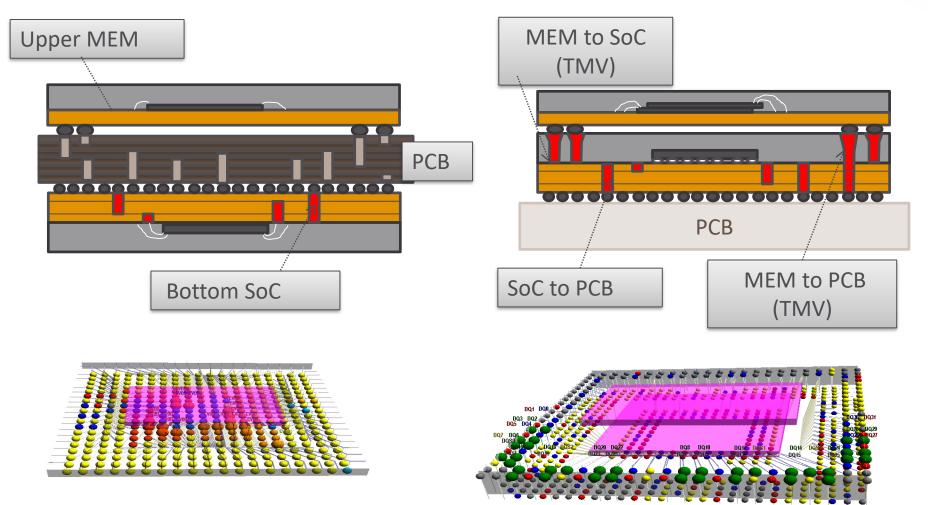

#### **GOING 3D – Package on Package**

E. Sicard, EMC performance analysis of a Processor/Memory System using PCB and Package-On-Package, EMC Compo 2015 Edinburgh

#### **GOING 3D – Stacked Dies**

# THERE IS PLENTY OF SPACE ON THE TOP

- 3D technology uses stacked dies, through-silicon-vias

- Enables 10-20

Gb/s/pin at 1.0V

- Samsung 3D

(Galaxy 6) vs PoP

(Galaxy 5) :

30% faster

- 20% less power

- Less heat

http://www.youtube.com/watch?v=Rw9fpsigCfk

de Toulouse

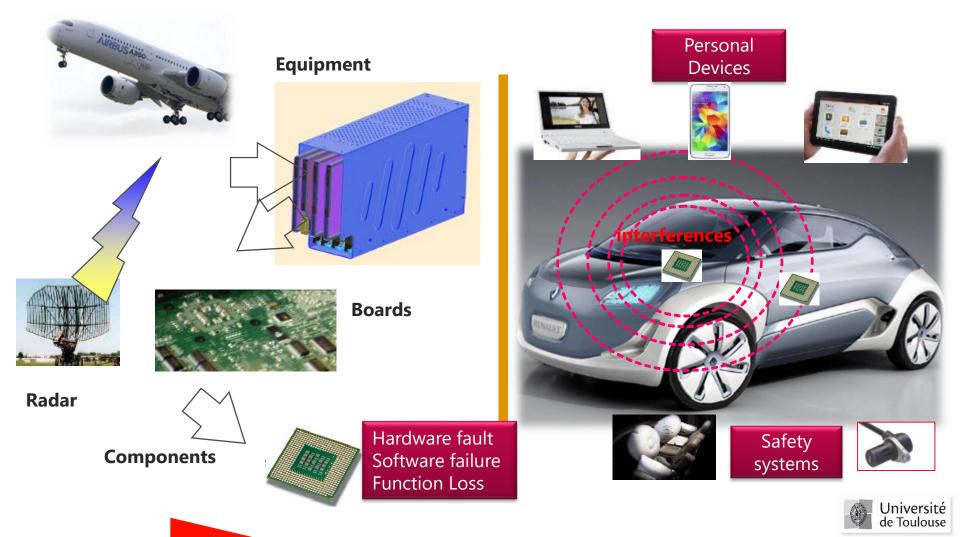

# 3 ELECTROMAGNETIC COMPATIBILITY

DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

**ONE ACRONYM – TWO PROBLEMS**

SUSCEPTIBILITY TO INTERFERENCE

EMISSION OF PARASITIC NOISE

Supply (V)

5.0

3.3

2.5

1.8

1.2

1.0

0.35µ

•

#### SUPPLY VOLTAGE SCALE DOWN

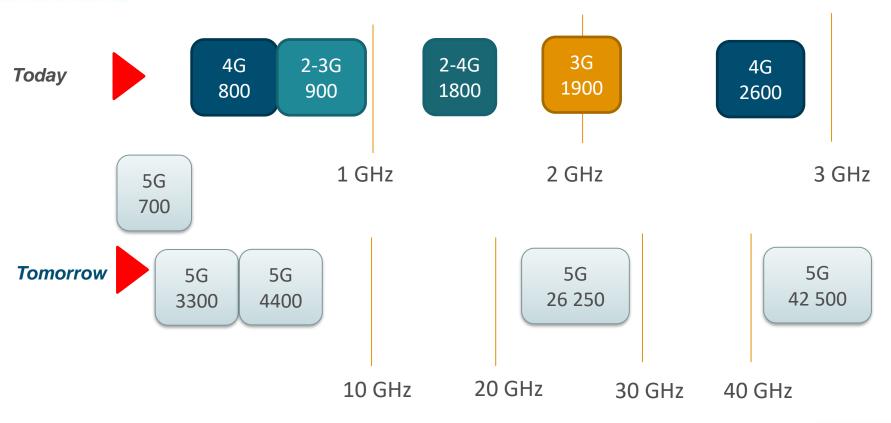

#### **HIGHER FREQUENCIES**

# 2,3,4,5G mobile frequencies

•

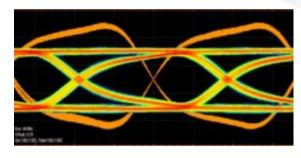

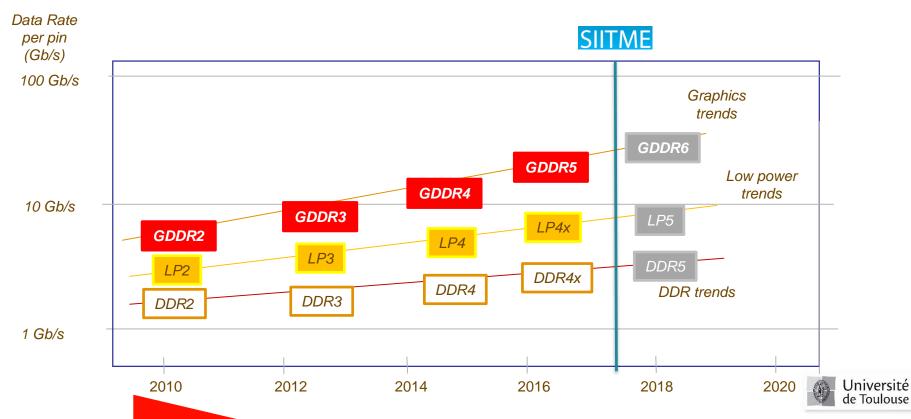

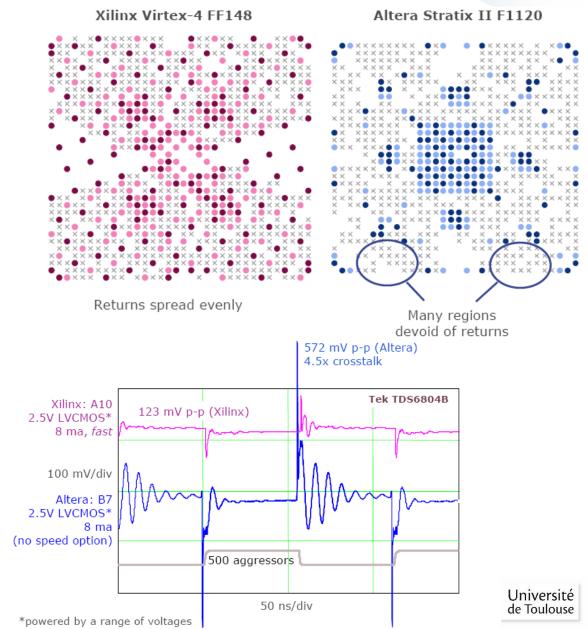

## **MORE I/O NOISE**

## I/O Technology

- Multi-Giga-Bit link between processors & memories : video, object recogn., 3D capture

- Generation 4x and 5 on the market

- Generation 6 under development

DDR4x: 230 ps, 0.25 V swing

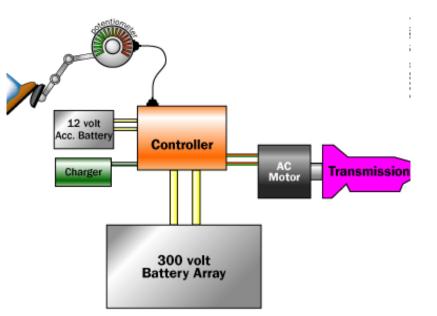

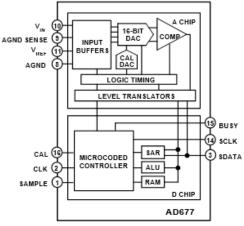

## WIDE RANGE OF OPERATING VOLTAGES

# Technology

- Nano-CMOS operates below 1V, noise margin around 50 mV

- Close to medium voltage (12, 24, 48

V) and high voltage (98, 240, 300, 400, 850 V) functions

- ADC with 16-24 bit resolution work at 10-100 µV resolution

# 4 DESIGN GUIDELINES

DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

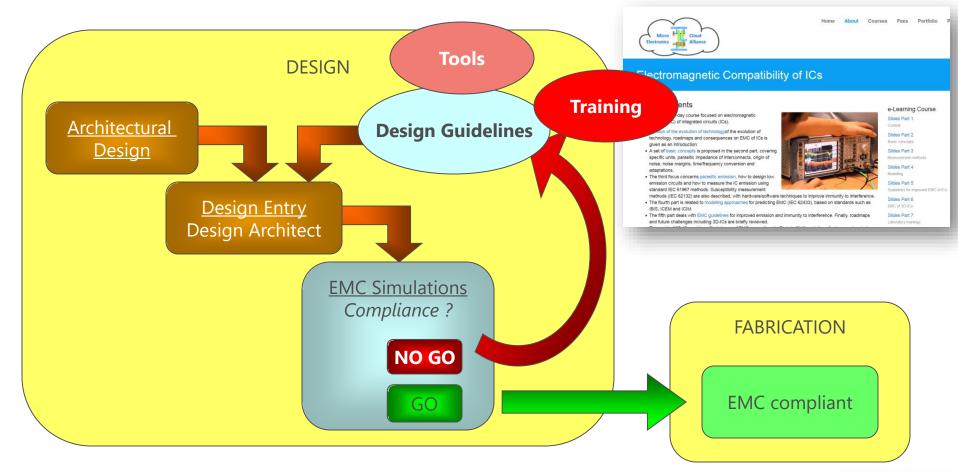

• Use tools, guidelines and trainings in EMC of Integrated circuits, for improved EMC before fabrication

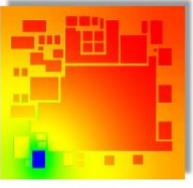

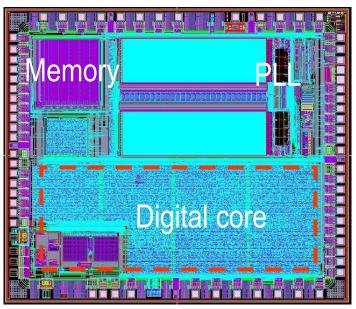

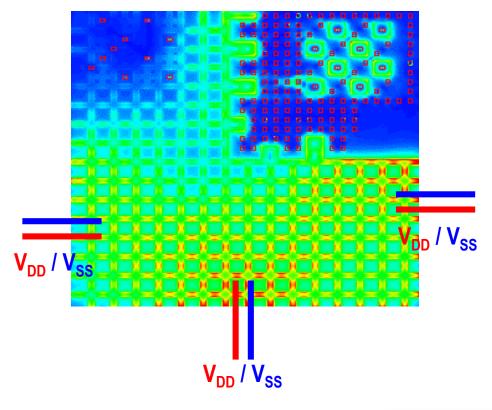

#### **DESIGN GUIDELINES - SUPPLY**

Place supply pairs close to noisy blocks

# Layout view

# **Current density simulation**

#### **DESIGN GUIDELINES - IOS**

for 10 IOs

27

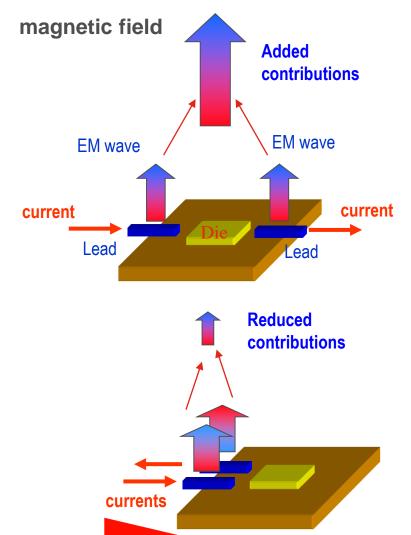

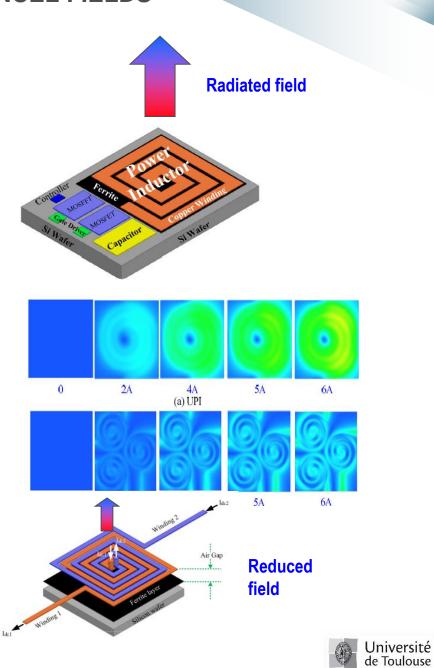

#### **DESIGN GUIDELINES – CANCEL FIELDS**

Reduce current loops that provoke

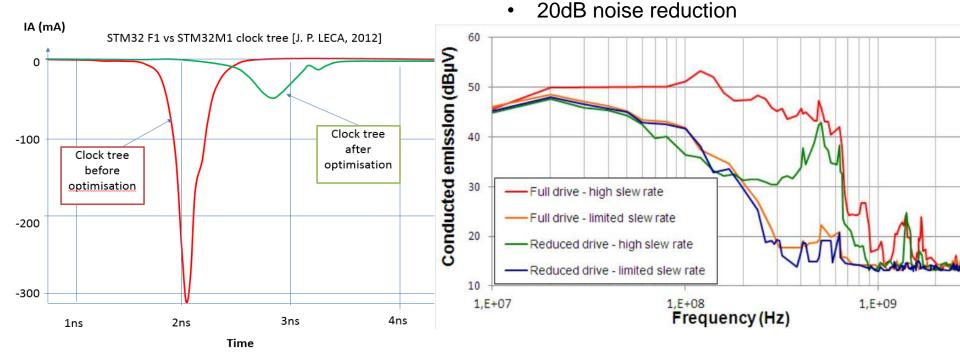

## DESIGN GUIDELINES – REDUCE SWITCHING NOISE

- Reduction of clock buffer's drive

- Spread of the switching

- 20dB noise reduction

- Reduce drive, limit slew rate,

- Adapt impedance,

- Add local decoupling

J-P. Leca "Microcontrollers Electromagnetic Interferences Modeling and Reduction",

PhD report, Univ of Nice, France, 2012

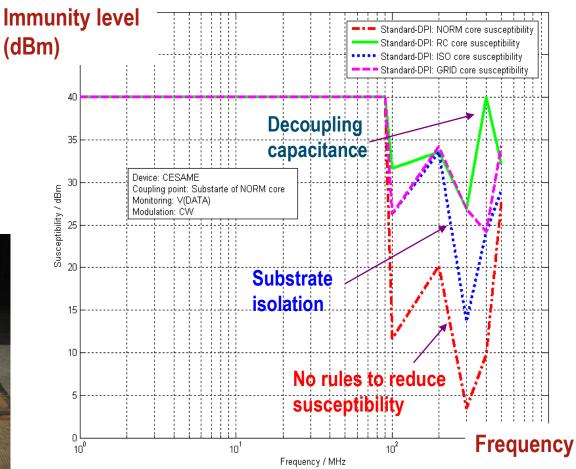

## DESIGN GUIDELINES – ISOLATE AND DECOUPLE

- On-chip decoupling

- Resistive supply path

- Substrate isolation

- Separate supply

- Separation between

incompatible blocks

Work done at Eseo France (Ali ALAELDINE)

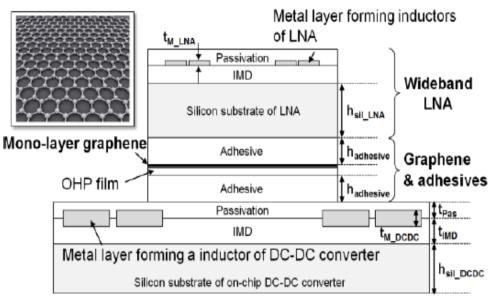

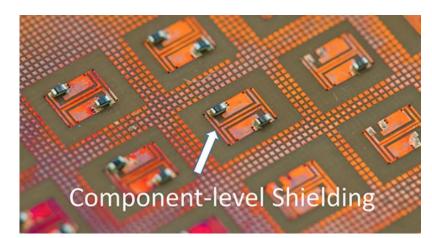

## **DESIGN GUIDELINES - SHIELDING**

- Graphene in stacked dies

- 10-15dB coupling reduction

On-chip switching DC-DC converter

K. Kim, "Graphene-based EMI Shielding for Vertical Noise Coupling Reduction in 3D Mixed-Signal System", 2012

- Thin magnetic-nonmagnetic multi-layered

structure

- Trench-via array and multi-layered conductor structures (5G, 28-39 GHz)

http://prc.gatech.edu/hg/item/585164

# CONCLUSION

DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

# CONCLUSION

- The electronic market growth should be driven by 5G mobile, automatic drive, Internet of Things, etc.

- The trends towards nano CMOS have been illustrated

- EMC concerns in terms of noise margin, higher frequencies and IO bandwidth

- Design guidelines for improved EMC have been introduced

#### www.ic-emc.org

# Thank you for your attention

# Special thanks to Prof. Norocel CODREANU, CETTI

DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING